Contact Information:

Research:

My research has been used and cited in many patents throughout the years by IBM, Google, Apple, Intel, Microsoft, Infineion, Micron, Canon, SUN Microsystems, Hitachi, and more.

Biography:

- Professor with the Department of Electrical, Computer and Biomedical Engineering (ECE), Toronto Metropolitan University, Toronto, Ontario, Canada.

- Nagi N. Mekhiel received the B.SC.Electrical Engineering degree (Communication) in Electrical Engineering from Assiut University, Egypt in 1973, and the M.A.Sc. from University of Toronto in 1981 and Ph.D. degree in Computer Engineering from McMaster University, Hamilton, Ontario, Canada in in 1995.

- He worked from 1981 to 1987 with the Hospital for Sick Children, Biomedical Research Institute, Toronto, Canada as a Biomedical Engineer, Designed microprocessor based systems for Chemotherapy, Antibiotic and Insulin infusion and licensed the System to Pancretec, a company in San Diego.

- In 1987 he joined Definicon Systems Corporation, Newbury Park, California, USA as a Senior Hardware Engineer to 1990, Designed Computer systems using AMD, SPARC and Motorola Processors, Published many design ideas for high performance memory that have been used in many patents until today.

- From 1996 to 1998, he worked with Yarc System Corporation Newbury Park, California, USA as a Senior Member of Technical Staff, Designed single and multiprocessor systems using Power-Pc for Image Processing.

- In 1997 he worked at University of California Santa Barbara, Santa Barbara, California, USA as a Lecturer in the Department of Electrical and Computer Engineering, Taught Fundamentals of Logic Design and Computer Organization.

- Dr. Mekhiel is a Senior Member of the IEEE.

Courses:

- bme328 Digital Systems (undergraduate)

- ees508Digital System for Aerospace Engineering

- coe608 Computer Organization and Architecture

- COE818 Advanced Computer Architecture (4th year elective)

- ee8218 Parallel Computing (graduate)

- coe758Digital Systems Engineering

Selected Publications:

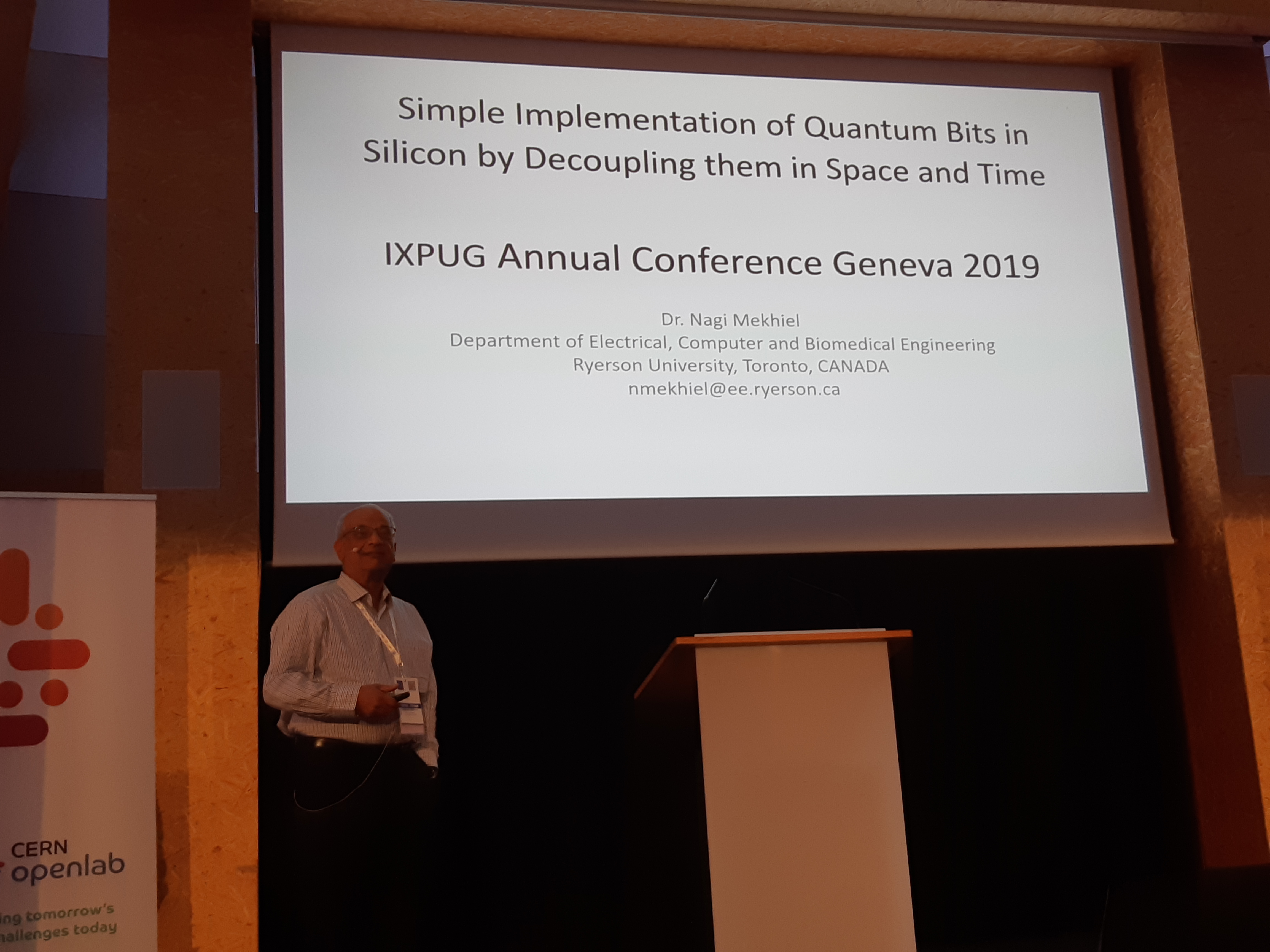

- presentation Intel eXtreme Performance IXPUG Sept 24-27, 2019 Conference, Geneva

Patents:

- Mekhiel, "Bandwidth Amplification Method Using Interleaving of Latched Data and Multi Phase Clocking," licensed to Intellectual Ventures US and filed for patenting in 2016. patent

- Mekhiel, "Reconfigurable ROW DRAM," licensed to Intellectual Ventures US and filed for patenting in 2016. patent

- Mekhiel, "Cache Filtering Method and Apparatus", Patent US2010/0070709 B2, Jan 7, 2014 (patent).

- Mekhiel, "Multi-Level Processing" Patent Application Nov 2010 (patent1 patent2).

- Mekhiel, "DATA PROCESSING WITH TIME-BASED MEMORY ACCESS" US 2009/0113159 (patent1 patent2).

- Mekhiel, "Methods And Apparatus For Accelerating Retrieval Of Data From A Memory System With Cache By Reducing Latency", Patent No: US 6,892,279 B2 May 10, 2005.

- Mekhiel, "Methods and apparatus for reducing latency in a memory system", Patent No: US 6,587,920 B2 July 1, 2003.

- Mekhiel, "Methods and apparatus for reducing latency in a memory system", Patent No: CA 2,327,134 Nov 30, 2000.

- Mekhiel, "Methods and apparatus for reducing latency in a memory system", Patent No: EP 1998894.8 Nov 28, 2001.

- Mekhiel, "Methods and apparatus for reducing latency in a memory system", Patent No: JP 2002-547003, Nov 28, 2001.

- Mekhiel, "Method and apparatus for reducing latency in a memory system by interleaving SRAM and DRAM accesses", United States Patent 20030200408, 10/23/2003. (patent1 patent2 patent3 patent4 patent5 patent6)

My Patents have been used in several industries:

- IBM Personal Computer

- IBM US7584335,09/01/2009

- Intel, US patent 6769047, July 27, 2004

- Micron Technology US 6804750, October 12 2004

- Canon, US 7149850 December 12, 2006

- Sun Microsystems, US 7571188 , 08/04/2009

- Infineon Technologies AG US 7127553, 10/24/2006

- Microsoft Corporation US 6473769 10/29/2002

- Microsoft Corporation US 679568 09/21/2004

- Microsoft Corporation US 6304879 10/16/2001

- Microsoft US Patent 6473769 Oct 29, 2002

- Hitachi Ltd, US 6154807 11/28/2000

- Hitachi LTD, US 6260107 07/10/2001

- Hitachi LTD, European Patent EP0809252 11/26/2003

- Renesas Technology Corp. (Tokyo, JP) US 7143230 11/28/2006