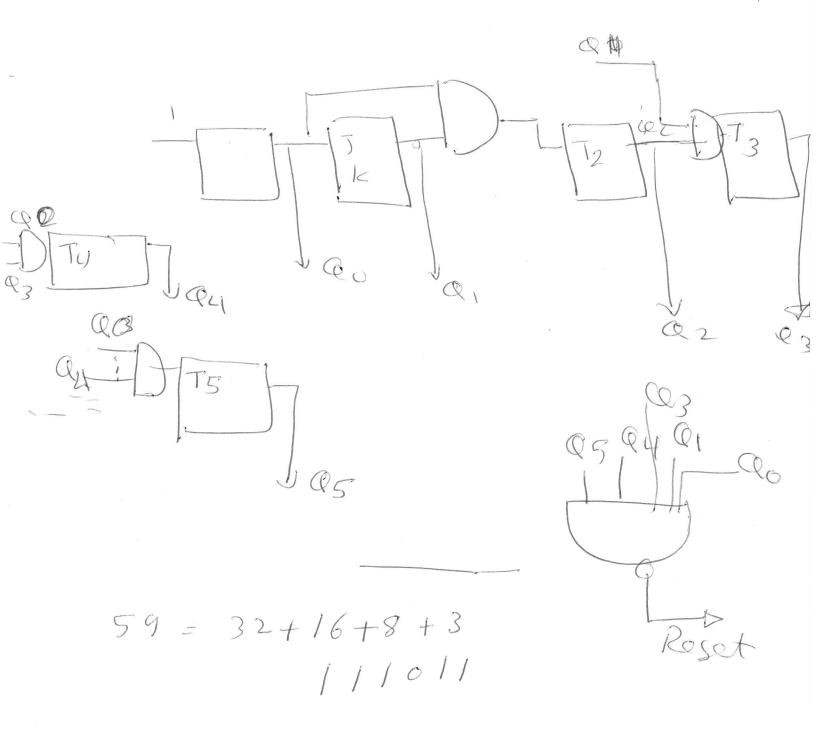

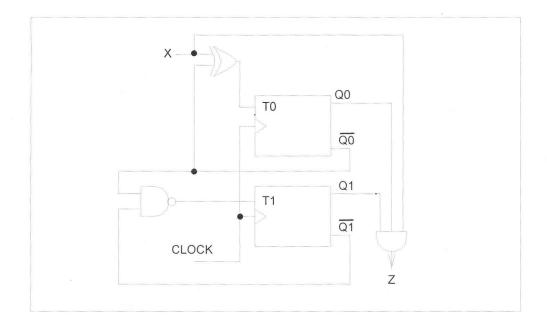

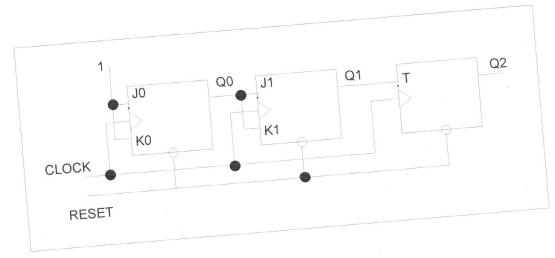

## 1. In the circuit below:

- a) Is the design a MOORE or Mealy Model

- b) Drive the state table assuming the states are: S0=00, S1=01, S2=10, S3=11

- c) Draw the state diagram showing the state, input and output.

@ Menly Design

| Page | 3 |

|------|---|

| rage | ) |

Section:\_\_\_\_

.

Name:\_

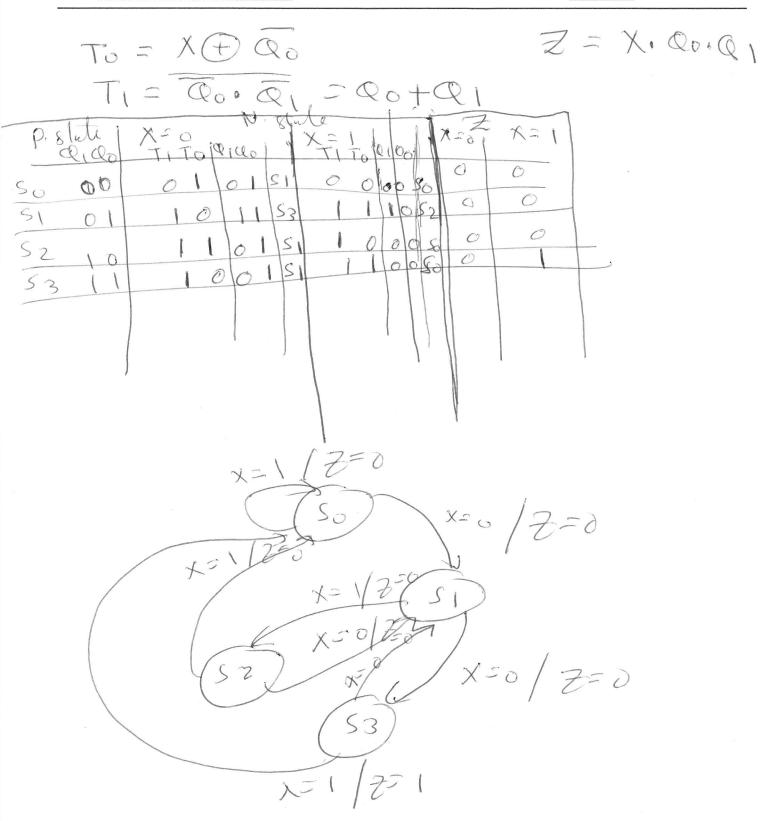

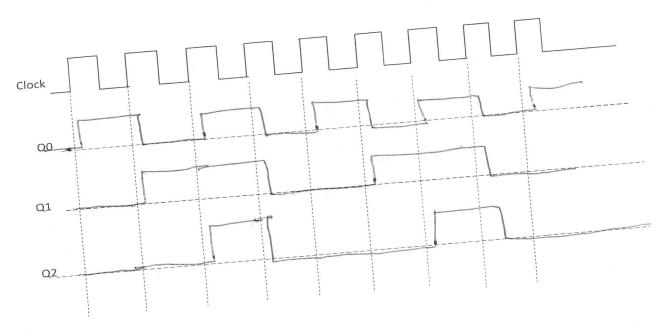

2. Given is the following timing diagram, clock signal, and input waveforms:

- a) Derive the state-assigned table.

- **b)** Draw the state diagram

c) Drive the circuit that implement the FSM

(??marks)

(?? marks)

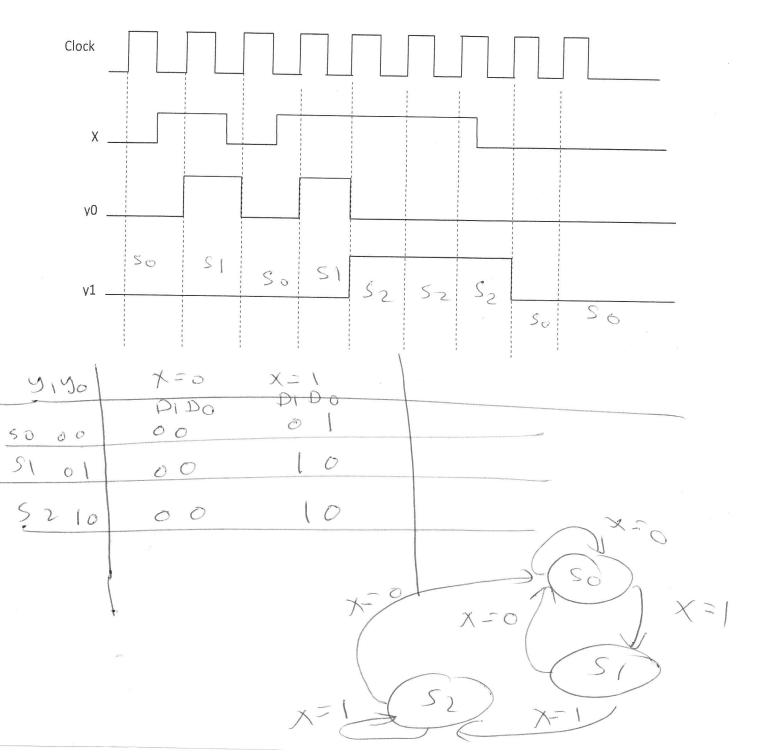

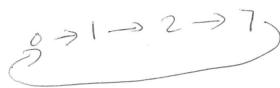

- 3. Following circuit is a counter

- a) Complete the timing diagram of the counter starting from  $Q_2Q_1Q_0=000$

**b)** Change the design of the counter to a modulo-59 counter.